- Home

- About

- Contact

- Blog

- Download minicom

- Signal probe on logicworks 5

- Xbox controller keymapper

- Winx hd video converter deluxe mkv

- Jason digital lab master mines

- Parallels desktop activation key

- Linkedin one click apply

- Pirates 2005 free download direct link

- Lilac ivory silk tree

- 8 ball quick fire pool

- Image file converter

- Oxygen forensic 2014 keygen

- -- edius pro 7

- Signal probe on logicworks 5 how to#

- Signal probe on logicworks 5 install#

- Signal probe on logicworks 5 manual#

- Signal probe on logicworks 5 full#

- Signal probe on logicworks 5 software#

Liveness probesĪ liveness probe checks whether the container is still running. A failed readiness probe means that a container should not receive any traffic from a proxy, even if it is running. The system stops sending traffic to the pod until it passes the readiness probe. When a pod is not ready, it is removed from the service's load balancers. One way to use this signal is to control which pods are used as service back ends. A pod is considered ready when all of its containers are ready.

Adding a readiness probe lets you know when a pod is ready to start accepting traffic. Readiness probesĪ readiness probe checks whether the container is ready to handle requests. OpenShift 4.5 offers three types of health checks to support application reliability and uptime: readiness probes, liveness probes, and startup probes. OpenShift already restarts pods when they crash, but adding health checks can make your deployments more robust. The system should also bring the application back up to a healthy state. You will need to re-route those requests to another instance of the app or have them re-tried at a later time. If an instance of your application isn't working, other services should stop accessing it and sending it requests. You can use health checks to automatically determine if your application is working. If you want to learn more about what's new and updated in OpenShift 4.5, read What’s new in the OpenShift 4.5 console developer experience.

Signal probe on logicworks 5 how to#

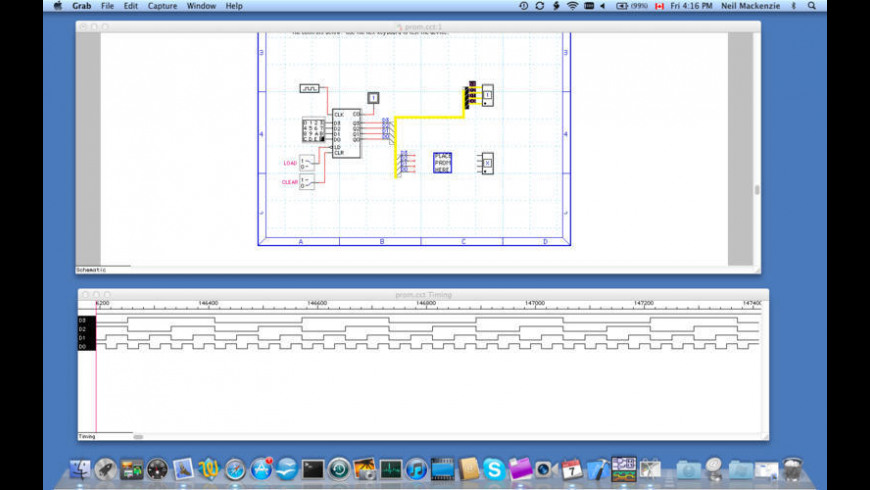

In this article, you will learn how to use health checks to improve application reliability and uptime in Red Hat OpenShift 4.5. Ideally, all of this should happen automatically. If one piece breaks, the system must be able to detect the issue and operate without that component until it is repaired. Print the schematic and the timing diagram.For an enterprise application to succeed, you need many moving parts to work correctly. You should try using the option of entering the stimulus waveforms on the timing diagram. Test the designed circuits using the LogicWorks software. Extend your design to build a 2-bit adder using EX-OR and NAND gates. Give a suitable implementation for this circuit.

Signal probe on logicworks 5 full#

Table 1 gives the truth table for a one-bit binary full adder, illustrated in Figure 3.

Show by simulations that the output is 0 for all possible input combinations. The output of the checking circuit is one if the two circuits are not the same. Design a network that checks simultaneously if the circuit in Figure 1 and its minimal NAND implementation perform the same function.

Signal probe on logicworks 5 software#

Can you get it down to four gates? Use the LogicWorks software to show that the two circuits are equivalent.į. Derive the truth table and implement the circuit using as few NAND gates as possible. The Exclusive-Or (EX-OR) gate network and its symbol are shown in Figure 2. Show by simulations that the circuit is equivalent to the circuit in Figure 1.Į. Draw an equivalent circuit of the network using a minimum number of NAND gates (use 2-input NAND gates only). See page 160 for a discussion of the even-driven nature of the simulator.ĭ. An event is the changing of the value of any signal. To actually make the timing diagram activate, you need to cause an event to happen. (Note that if the label is not properly attached, no signal is shown in the timing diagram window.) Repeat the testing as in step b), and observe the timing diagram. Label the inputs and the output (ref: Naming a signal, pg. Test the truth table by setting the switches to all possible combinations.Ĭ. 55) and a binary probe to the output (ref: pg. Connect a binary switch (from the primio library) to each input (ref: pg. Draw the network using the LogicWorks software, specifically using the primgate library. Derive the truth table for the logic gate network shown below in Figure 1:ī. Read the remainder of chapter 4, which has more useful details on schematic entry and simulation.Ī.

Do the "five minute" tutorial on pages 47-63.Ĥ. Read through the "User Interface" chapter, page 27 for Windows and page 37 for Macintosh.ģ.

Signal probe on logicworks 5 install#

Install the logicworks software onto your computer, following the instructions on page 13 for Windows machines, and page 18 for Macintosh machines.Ģ.

Signal probe on logicworks 5 manual#

Note: All page references are to the manual for LogicWorks 3.ġ. Bring the results of this exercise to that lab with you, as it will be checked as part of your preparation. This exercise should serve as an introduction to Lab #1. Printing out schematics and timing diagrams. Entering stimulus waveform using timing diagrams.Ĥ. Observing behaviour using timing diagrams.ģ. By the end of this exercise you should be familiar with:Ģ. Objective: To introduce the LogicWorks simulator. ECE241F Logicworks exercise ECE241F Logicworks exerciseĭepartment of Electrical and Computer Engineering